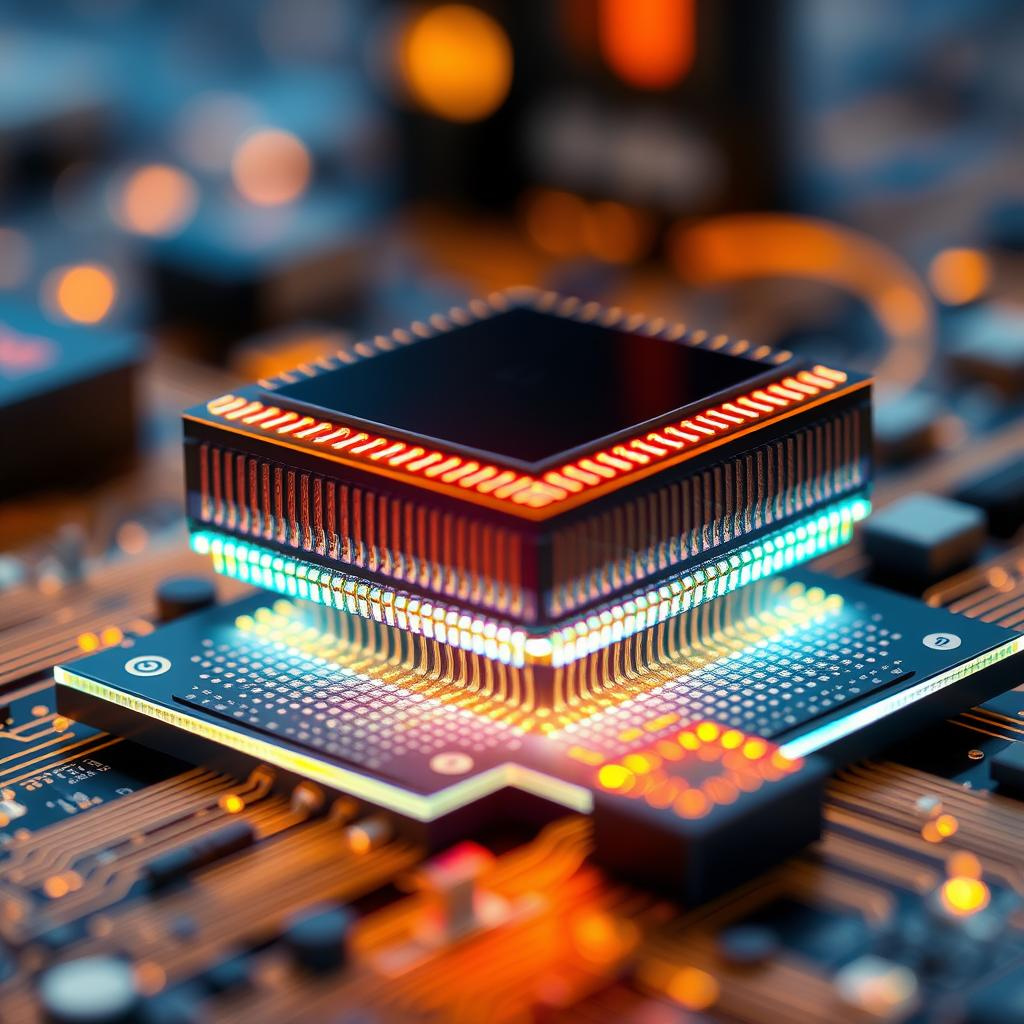

新材料有望提升微電子能源效率

麻省理工學院(MIT)研究團隊研發出一種創新製造方法,能夠將多個功能元件堆疊於現有電路之上,從而製造出更節能的電子裝置。

傳統電路中,執行運算的邏輯元件(如電晶體)與儲存資料的記憶元件是分開製作,資料在兩者間來回傳輸,導致能源浪費。這項新技術則讓科學家能在半導體晶片上將電晶體與記憶元件堆疊成一個緊湊結構,減少資料傳輸距離,降低能量損耗並提升計算速度。

這項突破的關鍵是新開發的材料——非晶氧化銦(amorphous indium oxide),以及更精準的製造工藝,能大幅減少材料缺陷,使得製作極小型且具備內建記憶功能的電晶體成為可能。這些電晶體的運作速度快於現有主流裝置,且耗電量更低。

隨著生成式人工智能、深度學習和電腦視覺等對計算能力需求激增,電子裝置的能源消耗也急劇增加。MIT博士後研究員邵延杰指出:「未來我們必須盡量減少人工智能等資料密集型運算的能耗,這種整合平台技術將是持續進步的關鍵。」

顛覆傳統問題的解決方案

標準CMOS晶片分為前端製程(製造電晶體和電容等活性元件)及後端製程(連接元件的導線與金屬鍵合)。資料在這些連接線間傳輸時會有能量流失,且微小的位移可能影響效能。若能將活性元件堆疊,資料傳輸距離縮短,晶片的能源效率將大幅提升。

然而,傳統上難以在CMOS晶片的前端堆疊矽電晶體,因為高溫製程會破壞下層的電晶體。MIT團隊改變思維,將活性元件堆疊於晶片後端,利用非晶氧化銦作為後端電晶體的活性通道層。此材料能在約150攝氏度的低溫下生長,避免損壞前端元件。

精密製程打造高效能元件

製程中,團隊精心優化以減少厚度僅約2納米的氧化銦層中的缺陷。適量的缺陷(氧空位)有助電晶體開關,但過多則會影響功能。這種優化讓電晶體能快速且穩定地切換,節省大量切換能耗。

在此基礎上,研究者還製造出約20納米大小的後端記憶電晶體,內含鐵電性鉿鋯氧化物作為記憶元件。這些元件切換速度達到10納秒,已接近測量儀器的極限,且所需電壓遠低於同類產品,進一步降低電力消耗。

由於記憶電晶體體積微小,團隊能以此研究鉿鋯氧化物的基本物理特性。邵延杰認為,更深入理解這種材料的物理特性,將開啟更多創新應用,因為它能在極低能耗下提供設計上的高度彈性,為未來裝置設計帶來無限可能。

此外,MIT與滑鐵盧大學合作,建立了後端電晶體的性能模型,為日後將元件整合入更大規模電路與系統鋪路。

未來目標包括將後端記憶電晶體整合到單一電路中,提升元件效能,以及精細調控鐵電性鉿鋯氧化物的特性。邵延杰表示:「我們已擁有高效能、功能多樣的後端電子平台架構與材料,但仍需不斷創新,挖掘其極限性能。」

此項研究獲得半導體研究公司(SRC)和英特爾部分資助,製造工作在MIT微系統技術實驗室及MIT.nano設施完成。

—

評論與啟示

這項MIT團隊的創新技術,從根本上改變了晶片元件的製造與整合方式,為微電子領域帶來一場潛在的革命。過往晶片設計面臨的能量浪費問題,源自於元件間物理距離與製程限制,這次透過低溫堆疊技術成功解決,極大減少了能耗與延遲,對推動AI、大數據等高性能計算的可持續發展意義重大。

尤其在全球能源危機與氣候變化的當下,電子設備的能源效率提升不僅是技術問題,更是環境與社會責任。MIT的成果展示了材料科學與製造工藝的深度融合,如何實現功能與效率的雙贏,這種跨領域整合是未來科技發展的關鍵。

此外,利用鐵電材料打造記憶與邏輯一體化的元件,為晶片設計帶來更多彈性與可能性,未來或許能催生更小型化、智能化的電子產品,甚至改變目前的計算架構。

然而,從實驗室突破到商業化量產仍有挑戰,包括製程穩定性、成本控制及與現有生態系統的兼容性。業界需密切關注此技術的演進,並積極投入研發與標準制定,確保新材料和製程能夠順利推廣。

總的來說,這項研究不僅是微電子技術的進步,更是能源可持續發展路上的重要里程碑,值得全球科技界與產業界深思與借鑒。

以上文章由特價GPT API KEY所翻譯及撰寫。而圖片則由FLUX根據內容自動生成。

![[Enhanced Artistic Prompt]

A highly detailed portrait of a young Asian woman inspired by the delicate, doll-like beauty of Imada Mio (精緻洋娃娃臉). She has large, round, luminous eyes with a deep, expressive gaze, a petite V-shaped face, full rosy cheeks, and porcelain-soft skin. Her expression is a captivating blend of innocence, youthful energy, and subtle flirtation, capturing an aura of pure allure.

Her hair is long, dark chocolate brown, with natural volume and texture—slightly tousled in an artful, “just woke up” messy style (剛睡醒的凌亂感), with soft strands falling over her face and shoulders. She wears an oversized, semi-translucent white button-down boyfriend shirt (男友風白襯衫), loosely draped and unbuttoned at the top, elegantly revealing her collarbones and creating a “bottomless” fashion look (下衣失蹤風格) with a sense of relaxed intimacy.

The overall aesthetic is reminiscent of a contemporary Japanese Gravure photobook (寫真集風格), evoking both pure charm and subtle sensuality (Pure & Sexy vibe). Use bright, high-key natural lighting to create a soft, ethereal glow, with smooth, radiant skin texture. Emphasize pastel color grading and gentle film grain, referencing the signature look of Fujifilm PRO 400H for a dreamy, cinematic finish. Compose the image artistically, focusing on beauty, mood, and expressive detail, as if captured in a candid, intimate moment.

— full body or mid-length portrait, shallow depth of field, delicate highlights, softly blurred minimalist background, inviting eyes, tasteful and elegant composition.](https://ssfuture.shop/wp-content/uploads/ai_gen_1764974976-300x300.png)